### DEVELOPMENT OF CMOS COPLANAR WAVEGUIDE MATCHING CIRCUIT FOR RF FRONT-END

### H. KANAYA, G. URAKAWA, R. OBA and K. YOSHIDA

Department of Electronics, Graduate School of Information Science and Electrical Engineering, Kyushu University, Fukuoka 812-8581, Japan E-mail: kanaya@ed.kyushu-u.ac.jp

For realizing a single chip microwave front-end, we studied the new design theory of impedance matching circuits for a Si-CMOS low noise amplifier (LNA) or power amplifier (PA), which are composed of coplanar waveguide (CPW) meanderline resonators and impedance inverters. We also present the simulated performances of CMOS-LNA or PA connected with input and output matching circuits. Finally, we designed the trial chip for 2.4GHz wireless LAN (IEEE 802.11b) system.

### 1. Introduction

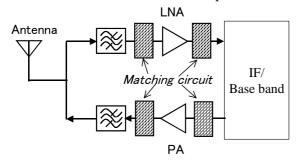

There are many location-free data translations, such as wireless LAN, bluetooth, IMT-2000 and satellite telecommunications. In order to make size reduction and cost performance, there are great expectations of a single chip RF-CMOS LSI, which is composed of low noise amplifier (LNA), power amplifier (PA), mixer, and so on [1]. Fig.1 shows the typical block diagram of RF section of the wireless terminal. Impedance matching circuit is necessary for interconnecting above devices. Although the lumped element circuits such as the spiral inductor and MIM capacitor are adopted for matching circuit [2], it cannot be used at high frequency range because of the self-resonance and stray impedances. On the other hand, distributed elements made of transmission lines are particularly effective because their size becomes smaller, as the higher. Moreover, coplanar frequency is waveguide (CPW) is easy to fabricate on the CMOS chip because the signal line and ground plane exist only on the same side, and also easy to realize desired characteristic impedance.

Fig.1. Brock diagram of the RF front-end.

In our previous papers [3,4], we proposed a new design method of the broadband impedance

matching circuit for the small antenna. In this paper, we generalize the design method of the on-chip matching circuit connecting with the LNA or PA. The circuit simulator and electromagnetic field simulator studies provide the expected performances of the LNA or PA with the input and output impedance matching circuit.

### 2. Design of CMOS low noise amplifier (LNA)

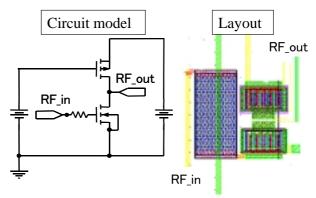

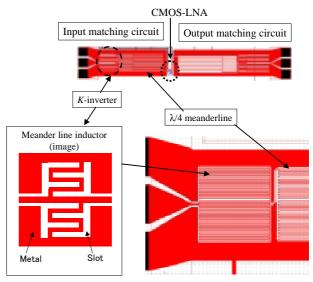

Fig.2 shows the schematic diagram of low noise amplifier (LNA). The gate length is  $0.25\mu m$  and VDD is 2.5V. The characteristics are simulated by the ADS (Agilent technologies).

Fig.2. Circuit model and tayout of LNA (0.25µm process).

The noise figure (F) is calculated as,

$$F = 1 + \frac{1}{G_S} \left( G_n + R_n | Y_S + Y_C |^2 \right) = F_{\min} + \frac{R_n}{G_S} | Y_S - Y_{opt} |^2$$

(1)

$$F_{\min} = 1 + 2R_n (G_C + G_{opt})$$

(2)

where,  $Y_{\text{opt}} = G_{\text{opt}} + jB_{\text{opt}}$   $G_{\text{opt}} = (G_{\text{c}}^2 + G_{\text{n}}/R_{\text{n}})^{1/2}$  and  $B_{\text{opt}} = -B_{\text{c}}$ .  $F_{\text{min}}$ ,  $R_{\text{n}}$  and  $Y_{\text{s}}$   $(=G_{\text{s}} + jB_{\text{s}})$  are the

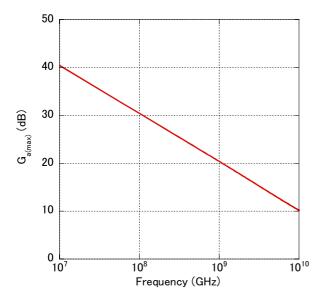

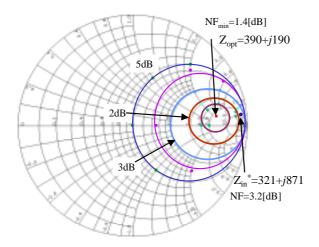

noise figure, equivalent noise minimum resistance and source admittance, respectively. In the noise simulation, we suppose that  $Y_c$ (correlation admittance)  $(=G_c+jB_c)$ apploximated to  $Y_{in}$  (input admitance) [5]. The simulated maximum available power gain  $(G_{a(max)})$  and the noise circle of LNA are shown in Fig.3 and Fig.4, respectively. At 2.45GHz, we obtain  $Z_{\text{opt}}=390+j190$  ( $\Omega$ ), where  $Z_{\text{opt}}$  $(=1/Y_{opt})$  is the impedance which minimize the Also, the input and output noise figure. impedances are  $Z_{in}=321-j871[\Omega]$  and  $Z_{out}=133$  $i121[\Omega]$ , respectively.

Fig.3. Frequency dependence of the maximum available power gain.

Fig.4. Noise circle at 2.45GHz.

## **3.** Design theory of on chip impedance matching circuit

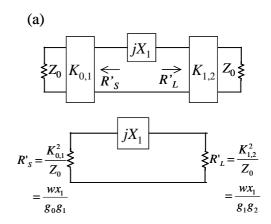

Fig.5(a) shows the circuit model of the 1-pole

BPF. In this figure,  $Z_0$ , w and  $g_i$  are the characteristic impedance of the transmission line, normalized bandwidth and normalized filter element, respectively. The reactance (X) and the reactance slope parameter (x) are for the series resonance circuit. At the resonant frequency ( $\omega_0$ ), the impedance inverters (K-inverters) of the 1-pole BPF are given by [4],

$$K_{0,1} = \sqrt{w} \sqrt{\frac{Z_0 x_1}{g_0 g_1}},$$

$$K_{1,2} = \sqrt{w} \sqrt{\frac{x_1 Z_0}{g_1 g_2}}, \quad X_1 = x_1 \left(\frac{\omega}{\omega_0} - \frac{\omega_0}{\omega}\right)$$

(3)

Fig.5. Circuit models of (a) 1-pole bandpass filter and (b) quarter wavelength matching circuit.

Fig.5(b) shows the circuit model of the quarter wavelength matching circuit. In the figure,  $Y_L$  (= $G_L$ + $jB_L$ ) and  $Z_1$  are the input impedance of the LNA and characteristic impedance of the quarter wavelength line, respectively. In order to compensate the  $jB_L$ , we adjust the length by  $\Delta \ell$  as (see Fig.5(b)),

$$\Delta \ell = -\frac{B_L}{\omega_0 C} \,, \tag{4}$$

where, C is the capacitance per unit length of the transmission line. Finally, by comparison of the  $R'_s$  and  $R'_L$  in the Fig.5(a) and (b), the proposed design values for the K-inverter and  $Z_1$  are given by.

$$K_{0,1} = \sqrt{w} \sqrt{\frac{Z_0 x_1}{g_0 g_1}}, \quad \left(x_1 = \frac{\pi}{4} Z_1\right), \quad Z_1 = \frac{\pi}{4} \frac{w}{g_1 g_2 G_L}.$$

(5)

In the case of noise matching, it is easy to show  $Z_L=Z^*_{\text{opt}}$  in eqs. (4) and (5).

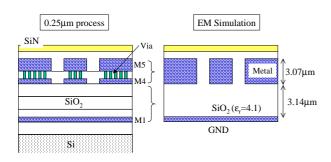

# 4. Layout of LNA connected with CPW input and output impedance matching circuit

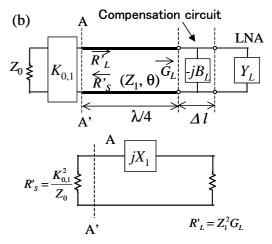

Fig.6 shows the sectional views of the CPW structure and EM-simulated condition of the CMOS chip. This chip has a 5-metal layer structure. In order to avoid the loss in the Si, we covered the lowest metal (metal1), namely conductor backed CPW. For suppressing the conductor loss, metal4 and metal5 are connected with a large number of vias, where a conductance of the metal is  $4.1 \times 10^7$  S/m in this simulation. The signal width and the interval between the slots of the  $50\Omega$  line are  $5\mu m$  and 13µm, respectively. The EM simulated quality factor of the CPW straight resonator is  $Q_u$ =68 at For size reduction, the quarter 2.45GHz. wavelength line was bended into meander The design parameters of the structure. matching circuit are  $f_0=2.45$ GHz, w=100MHz (IEEE 802.11b). Fig. 7 shows the layout of the quarter wavelength impedance matching circuit on the Si substrate. K-inverter is fabricated by using shunt meander inductor. The chip aria of the input matching circuit is 0.2mm<sup>2</sup>, which is 40% as small as that of the spiral inductor (lumped element).

Fig.6. Sectional views of the real process and EM-simulated condition.

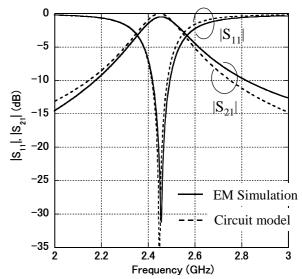

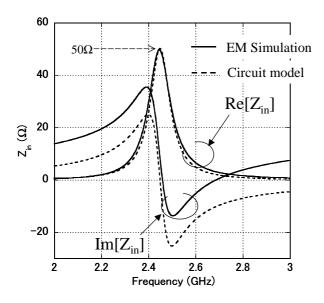

Fig. 8 shows the EM simulated input return loss and insertion loss of the matching circuit. Fig. 9 shows the frequency dependence of the input impedance. The return loss ( $S_{11}$ ) and the input resistance are almost similar to the data calculated from eq. (5) (theoretical curve). Although, the insertion loss in the passband appears because of the metal loss, the  $R_{\rm in}$  and  $X_{\rm in}$  are matched to  $Z_0$  (=50+ $j0\Omega$ ) at the center frequency.

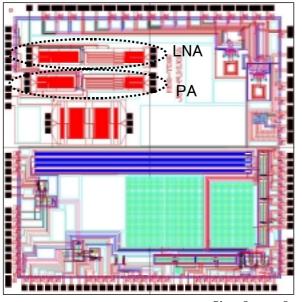

Fig. 10 shows the chip layout of the LNA and PA with input and output impedance matching circuit, namely there are 4 matching sections. The chip size is 5mm x 5mm. The input and output port are connected with the CPW pads for measuring.

Fig.7. Layout of input and output matching circuit connected with LNA.

Fig.8. Simulation results of *S* parameters.

Fig.9. Frequency dependence of the input impedance.

Size: 5mm x 5mm

Fig.10. Chip layout of RF CMOS front-end.

#### 5. Conclusion

We designed the LNA and PA connected with input and output impedance matching circuit on the CMOS chip, which is composed of quarter-wavelength resonator and *K*-inverter. Our new transmission-line-based matching circuit is not only of the small size but also we can design the bandwidth, which is superior to the lumped element matching circuit. Moreover, we can adjust the meander-line shape in order to fit the vacant place on the substrate. We will evaluate the microwave characteristics of the trial chip.

### Acknowledgements

This work was partly supported by a Grant-in-Aid for Encouragement of Young Scientists (B) from the Japan Society for the Promotion of Science (JSPS). This work was partly supported by VLSI Design and Education Center (VDEC). the University of Tokyo in collaboration with CADENCE and SYNOPSYS Corporation. This work was partly in collaboration with Innovation Plaza Fukuoka, Japan Science and Technology Corporation (JST). This work was partly supported by the 21st Century COE Program 'Reconstruction of Social Infrastructure Related Information Science and Electrical Engineering'.

#### References

- [1] A. Matsuzawa, "RF-SoC-Expectations and Required Conditions," IEEE. Trans. Microwave Theory Tech., vol. 50, pp. 245-253, January 2002.

- [2] M. Ono, N. Suematsu, S. Kubo, K. Nakajima, Y. Iyama, T. Takagi, and O. Ishida, "Si Substrate Registivity Design for On-Chip Matching Circuit Based on Electro-Magnetic Simulation," IEICE Trans. Electron., vol. E84-C, pp. 923-929, July 2001.

- [3] K. Yoshida, T. Takahashi, H. Kanaya, T. Uchiyama, and Z. Wang, "Superconducting slot antenna with broadband impedance matching circuit," IEEE Trans. Appl. Supercond., vol. 11, pp. 103-106. March 2001.

- [4] H. Kanaya, Y. Koga, J. Fujiyama, G. Urakawa, and K. Yoshida, "Design and Performance of High Tc Superconducting Coplanar Waveguide Matching Circuit for RF-CMOS LNA", IEICE Trans. Electron., vol.E86-C, No.1, pp.37-41, January, 2003.

- [5] Y. Ando, "Noise in Microwave Devices", MWE'96 Microwave Workshop Digest, pp.473-482, 1996.