# Design of 1.1 GHz Highly Linear Digitally-Controlled Ring Oscillator with Wide Tuning Range

A. Tomar, R. K. Pokharel, O. Nizhnik, H. Kanaya, and K. Yoshida

Graduate School of Information Science and Electrical Engineering Kyushu University, Fukuoka 819-0395, Japan

Abstract: This paper presents a simple architecture for 8-bit digital controlled oscillator (DCO) on 3-stages ring topology in TSMC 0.35um CMOS technology. A new schematic of tristate inverter is also proposed. The proposed tristate inverter has higher switching speed and low power consumption as compared to conventional one. The control digit changes the driving current that provides large tuning range from 333 MHz to 1472 MHz with very good linearity. The output voltage swing is constant and above 3volt (>90% of the supply voltage i.e. 3.3V). The presented circuit shows the fast response to the output frequency transition and this takes less than one clock period and without showing any ringing or damping during frequency transition. The proposed DCO has simulated phase noise of -106dBc/Hz @1Mhz and 63.4 mw power consumption at 1.1 GHz central frequency.

*Index Terms* — ring oscillator, DCO, inverter, phase noise, linearity.

## I. INTRODUCTION

In recent years, CMOS technology is scaling down resulting to a very low control voltage that leads to the availability of only very steep slope [1], and this complicates the implementation of conventional RF circuits in CMOS technology, often causes instability and the portability issues. Furthermore, low voltage and thin metal interconnects which are achieved in a scaled-down CMOS process are advantageous to digital circuits but the same becomes disadvantages to RF circuits due to reduced voltage headroom, low inductor's quality factor, and reduced gate oxide reliability. Therefore, RF circuits such as RF oscillators need to be realized employing digitally controlled logics for future generation wireless technology.

In conventional wireless systems, two types of oscillators i.e. ring oscillator and LC-tank oscillator are often used to generate a local frequency in a phase-locked loop (PLL) [2]. The former is often used in MHz frequency applications because of its compactness, as spiral inductors are usually not necessary in a ring topology. In GHz frequency applications, the later is usually preferred because of its improved noise performance and lower power consumption.

As a ring oscillator is more compact than LC-tank oscillator, designing a ring oscillator for GHz frequency applications is the main area of interest in this paper. In Ref. [3], the architecture uses transmission gate be-

tween inverter delay stages and vary the value of the resistance of the transmission gate with the control voltage applied to the transmission gate which has drawback of frequency saturation for higher voltages so that it provides low control voltage range. In Ref. [4], [5], digital control but asymmetrical stages were used which reduces the output voltage swing that makes the circuit sensitive to the phase noise. In Ref. [6], parallel resistors were used in transmission gate and control the resistance by changing digital control. It provides high load resistances means more power dissipation. And also resistance becomes saturated at high control logic so that linearity worsens.

This paper proposes a new architecture for 8-bit digitally-controlled ring oscillator. This architecture provides symmetrical load, high linearity and very large output voltage swing which overcomes the problem of Ref. [4], [5]. The output frequency of the DCO is controlled by the varying the driving current according to the input control bits.

# II. DESIGN OF CONVENTIONAL RING OSCILLATOR

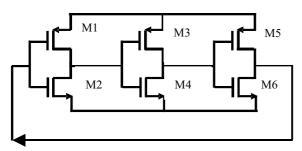

A basic ring oscillator uses odd number of inverters. An example of three-stages ring oscillator [2] is shown in Fig 1. Each inverter in the oscillator is used as a delay cell. The frequency of oscillation for identical cell is given by Equation (1).

$$f_{osc} = \frac{1}{2N T_d} \tag{1}$$

Where  $T_{\rm d}$  is the delay of each inverter cell and N is number of identical cell. From Equation (1), the period or frequency of oscillation is varied either by changing the number of inverter stages in the ring or varying the propagation delay of inverter. The delay of each inverter cell is further expressed as,

$$T_d = \frac{C_L \cdot \Delta V}{I_d} \tag{2}$$

Where  $C_L$  is load capacitance,  $\Delta V$  is the output voltage swing and  $I_d$  is the driving current to the load. It is clearly noted from the Equation (2) that the frequency

of oscillation without changing number of stages can be varied either by changing the load capacitance or driving current to the load. The propagation delay of inverter is proportional to Width to Length (W/L) ratio of the transistor as increment in width increases the capacitance and decreases the resistance that makes time constant equal and frequency remains constant. The load capacitance ( $C_L$ ) at the output node of inverter can be expressed by Equation (3) [7].

$$\begin{aligned} C_L &= C_{gsM3} + C_{gsM4} + C_{dbM1} + C_{dbM2} \\ &+ C_{gdM1} + C_{gdM2} + C_w \end{aligned} \tag{3}$$

Where, suffices g, s, b represent gate, source and body (substrate) of transistors M1, M2 and M3, respectively. Similarly, Cw represents wire capacitance. The load capacitance can be changed by using MIM capacitor or MOS transistor at the output node of inverter. But it cannot be much useful in sub-micron technology as wired capacitance have significant portion in load capacitance, which in turn, limits the maximum oscillating frequency [6] of an oscillator. Thus, this approach would not be much useful to achieve wide turning range of an oscillator. Controlling delay by changing the driving current ( $I_d$ ) would support for wide tuning range and also provides high linearity which is utilized in the presented DCO.

Fig. 1. 3-stages conventional ring oscillator [2].

## III. DESIGN OF PROPOSED DCO

# A. Topology of DCO

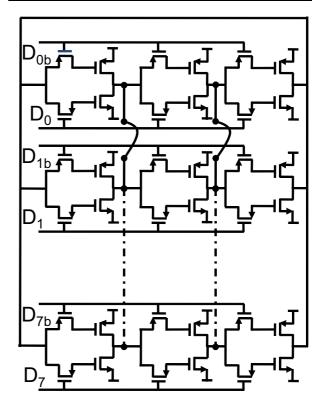

The schematic of the proposed 3-stages digital controlled ring oscillator is shown in Fig 2. The circuit has 8 control bits (D0-D7). All the stages are identical and make a ring for an individual bit. For 8 bits, 8 rings with different *W/L* ratio are made in parallel by connecting them at the output of each delay cell. Each ring is made with identical stages to provide equal delay. One of the advantages of the proposed method is that it provides symmetrical load unlikely in ref. [3-5]. The output frequency of the oscillator depends on the control bits. The proposed schematic has used newly proposed tristate inverter for the delay cell.

#### B. Tristate Inverter DCO Cell

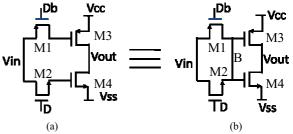

Fig. 3 shows the tristate inverter circuit used in the proposed DCO. The proposed tristate inverter uses four transistors whose numbers are equal to the conventional one but differs in topology. In conventional inverters, four inverters gate are connected in series.

In the proposed inverter, it has control input D that controls the signal propagation from input to the output through transistors M1 and M3 or M2 and M4 depending on the input level Low (0), High (1), respectively. When D=0, the output will no longer connected to the input and none of the transistors M3, M4 conducts. The size of the transistors are selected to provide equal delay through both the paths. The W/L ratio of all the transistors are listed in Table 1.

Table 1 Size of the transistors in tristate inverter.

| Name of     | M1  | M2  | M3  | M4  |

|-------------|-----|-----|-----|-----|

| Transistors |     |     |     |     |

| Size ratio  | 2.5 | 1.0 | 2.5 | 1.0 |

Fig .2. Schematic of proposed DCO

Fig. 3. Proposed tristate inverter (a) and its equivalent circuit when control bit is 1 (b).

The proposed tristate inverter cell can be approximated as transmission gate followed by an inverter when D=1. Equivalent circuit of the proposed inverter when D=1 is shown in Fig. 3(b).

For one delay cell calculation the signal starts propagating at node  $V_{\rm in}$  and terminates at node  $V_{\rm out}$  through node B. Hence, from the equivalent circuit of Fig. 3(b), the delay of the tristate inverter cell can be interpreted in to two parts: inverter delay and transmission gate delay. The total delay of the circuit is given by,

$$T_d = T_{INV} + T_{TG} \tag{4}$$

Hence, inverter cell delay ( $T_{INV}$ ) is calculated by Equation (2) where the driving current ( $I_d$ ) is given by Equation (5) for the proposed oscillator.

$$I_{d} = I_{0} \bullet \sum_{n=0}^{n=N-1} \left(\frac{W}{L}\right)_{n} B_{n}$$

(5)

Where  $I_0$  = Current flowing for W/L=1,  $B_n$  is the status of the control bits i.e.  $B_n$  =1 if switch is on, and  $B_n$  = 0 if switch is off. It was also explained before that output frequency is controlled by changing  $I_D$  in the proposed DCO as it provides high linearity for a very wide tuning range in comparison to the change in load capacitance as earlier employed in [4].

The transmission gate can be represented as a constant RC delay cell [7] where the delay for the transmission gates is given by,

$$T_{TG} = 0.69 R_{TG} C_{LB}$$

Where  $R_{TG}$  is the resistance of the transmission gate, approximately constant during switching but inversely proportional to the W/L ratio of the transistors and  $C_{Lb}$  is the load capacitance at the output node of transmission gate.

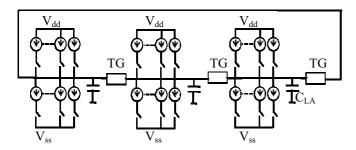

The equivalent circuit representing delay control mechanism of the proposed DCO is shown in Fig. 4 where inverter transistors are shown by current sources, transmission gate as a constant delay cell (TG) and control input is represented by switches in current sources. The load capacitance ( $C_{LA}$ ) of the inverter is constant because all the transistor are connected to that node irrespective of the number of control bits status. According to the control code (D0-D7), switches turns on or off and set the value of current which controls the delay and in turn, the oscillating frequency.

Fig. 4. Equivalent circuit of delay control unit.

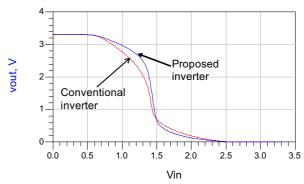

Fig. 5. Comparison of voltage transfer characteristics of the proposed tristate inverter and conventional tristate.

### IV. SIMULATION RESULTS

The proposed DCO was designed by means of ADS (Agilent Co., ADS 2004A) using TSMC 0.35 um CMOS process parameters, and supply voltage of this process is 3.3 V.

The comparison of voltage transfer characteristics of proposed and conventional tristate inverter circuit are plotted using same size transistor and same supply voltage in Fig. 5 where the proposed DCO has very sharp transition region. Simulated shows that proposed tristate inverter has 20-30% power reduction from 2GHz to 250MHZ frequency. It also shows the significant improvement of 10% in speed.

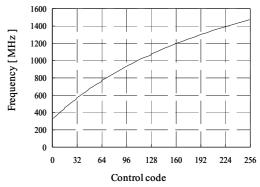

The proposed DCO was simulated for all the possible combination of control code. The frequency range of the DCO is from 333Mhz to 1472Mhz. The frequency versus input control words is shown in Fig. 6, where it is noted that the proposed DCO possess the high linearity for the wide range of frequency.

Fig. 6. Relationship between central frequency and input control code showing linearity of the designed DCO.

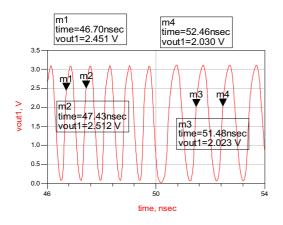

The simulated output waveform of the selected control input signal is shown in Fig 7. This clearly shows the large output voltage swing (>3V). The proposed DCO also changes the output frequency within one clock period without any ringing at the output voltage also output voltage swing is constant. Phase noise was

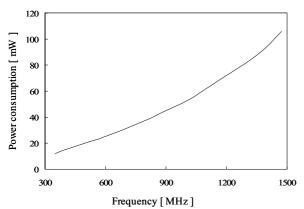

also calculated for the proposed circuit. The phase noise is -106dBc/Hz @1MHz at 1.1 GHz central frequency which is shown in Fig. 8. The dependence of power consumption with center frequency is shown in Fig. 9 where it draws total current of 19 mA for 3.3 V DC supply at 1.1 GHz frequency. The comparison of power consumption with other published DCOs on the similar technology was illustrated in Table 2 where the proposed DCO is least power consumption among three.

Fig 7. Transition of frequency from 1.3GHz to 1.02GHz.

Fig. 8. Simulated phase noise of the proposed DCO for 1.1 GHz central frequency.

Fig. 9. Dependence of power consumption on central frequency.

Table II Comparison of power consumption of the proposed DCO with other published works.

| Items       | Proposed | Ref. [5] | Ref. [8] |

|-------------|----------|----------|----------|

| Function    |          |          |          |

| Process     | 0.35μm@  | 0.35μm@  | 0.35μm@  |

|             | 3.3V     | 3.3V     | 3.3V     |

| Output      | 333-1472 | 18-214   | 45 - 450 |

| frequency   | (MHz)    | (MHz)    | (MHz)    |

| Power       | 17.5mW@  | 18mW@    | 100mW@   |

| consumption | 450MHz   | 200MHz   | 450MHz   |

#### V. CONCLUSION

A high-linearity 8-bit digitally-controlled oscillator (DCO) is designed on a ring topology using TSMC 0.35 um CMOS process parameters. One of the advantages of the ring topology over a LC-tank oscillator is that it does not contain any spiral inductor so that the chip size is very small. It consumes 19 mA current at 3.3 V supply voltage and simulated phase noise is -106dBc/Hz (@1MHz). Verification of the simulated results would be carried out in near future.

#### ACKNOWLEDGEMENT

This work was partly supported by a grant of Knowledge Cluster Initiative implemented by Ministry of Education, Culture, Sports, Science and Technology (MEXT). This work was also partly supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with CADENCE Corporation and Agilent Corporation.

#### REFERENCES

- A. Matsuzawa, "Analog IC technologies for future wireless systems," *IEICE Trans. Electron.*, vol. 89-C, no. 4, pp. 446-454, April 2006.

- [2] L. Dai and R. Harjani, Design of high-performance CMOS voltage controlled oscillator, Kluwer Academic Publishers, 2003.

- [3] R. A. Nicodimus, S. Takagi, and N. Fujii, "Wide turning range voltage-controlled ring oscillator," *IEICE Trans Electron.*, vol.-E86, no. 6, pp. 1085-1088, June 2003.

- [4] C.F. Chan, O.Choy. "A low power digital controlled oscillator" *INt.J. ELECTRONICS*.,pp. vol.88,no.4,463-466, 2001.

- [5] P.-L. Chen, C.-C. Chung, and C.-Y. Lee, "A portable digitally controlled oscillator using novel varactors," *IEEE Trans. on Circuits and Systems-II*, vol. 52, no. 5, pp. 233-237, 2005.

- [6] S. M. Rezaul Hasan, and Nazmul Ula, "A 16-bit CMOS digitally controlled oscillator using a novel control scheme," 49<sup>th</sup> IEEE International Symposium on Circuits and Systems (2006 MWSCAS'06), vol. 1, pp. 680-684, Aug. 2006.

- [7] J. M. Rabaey, Digital Integrated Circuits: a Design Perspective. Prentice-Hall, Inc., 1996.

- [8] C.C.Chung and C.-Y. Lee, "An all digital phase-locked loop for high speed clock generation," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 347-351, Feb.2003.